Application Note AN 96041

# **APPLICATION NOTE**

# APPLICATION INFORMATION FOR PICTURE IN PICTURE CONTROLLER SAB9077 AN 96041

Author(s): G. Bauhuis

Design & Application Department, Consumer ICs Nijmegen, The Netherlands

## Keywords

PIP Application Multi Window IIC Settings

Pages: 95

Date: April 1996

## Summary

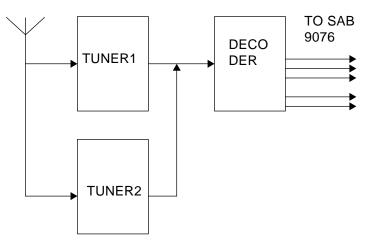

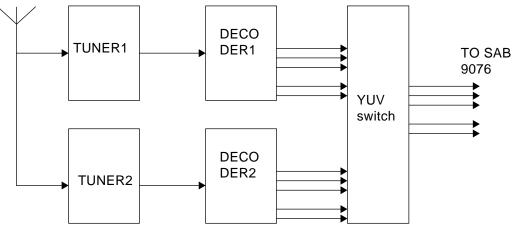

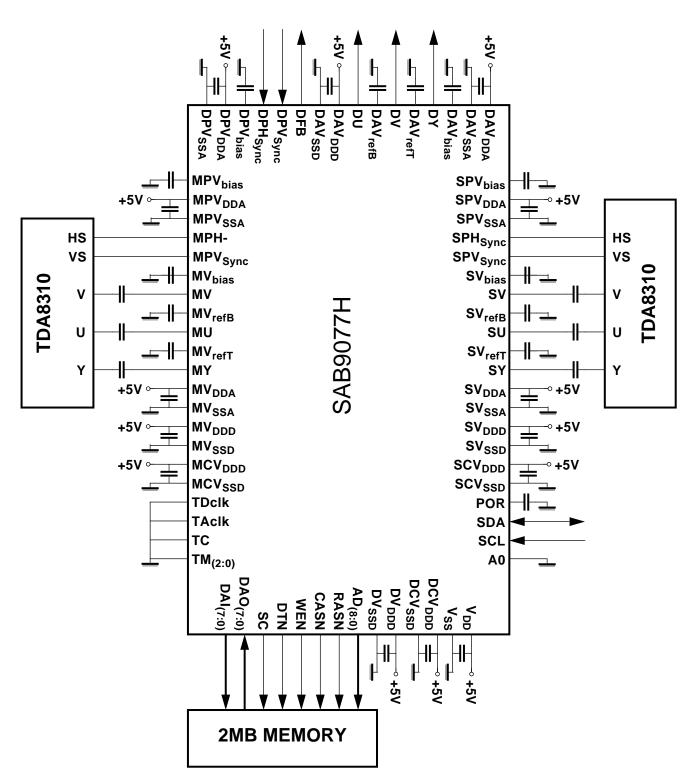

The SAB 9077H in combination with two Multistandard decoders TDA 8310 and a memory of type D 482234 LE-70 (NEC) provides a Picture in Picture (PIP) system for the Multistandard environment.

It delivers one or two live video signals with reduced sizes for a live or frozen video signal.

Because of the two PIP-channels and a large external memory a wide range of PIP-modes are offered. The emphasis is put on double PIP and multi-PIP modes. In combination with an input video selector and some IIC-Bus software the SAB9077 system can be used e.g. as a channel selection tool. The hardware and software requirements for a good use of the SAB9077 are specified in this application note.

| 6            |

|--------------|

| 7            |

| 8            |

| 9            |

| . 11         |

| . 12         |

| . 12         |

| . 12         |

| . 12         |

| . 12         |

| . 12         |

| . 14         |

| . 17         |

| . 17         |

| . 18         |

| . 19         |

| . 19         |

| . 19         |

| . 19         |

| . 19         |

| . 20         |

| . 20         |

| . 20         |

| . 20         |

| . 20         |

| . 22         |

| . 24         |

| . 24         |

| . 25         |

| . 26         |

| . 27         |

| . 27<br>. 27 |

| . 27         |

| . 27         |

| . 28         |

| . 20         |

| . 29         |

|              |

# Application Note AN 96041

| 9.2 | Data tr | ansfer settings                                | 30 |

|-----|---------|------------------------------------------------|----|

| 9.3 | Border  | settings                                       | 31 |

|     | 9.3.1   | Border ON/OFF                                  | 31 |

|     | 9.3.2   | Border color and brightness                    | 31 |

|     | 9.3.3   | border-size                                    | 32 |

|     | 9.3.4   | Border select                                  | 33 |

|     | 9.3.5   | Border priority                                | 34 |

|     | 9.3.6   | Polarity of the border and background colors   | 34 |

| 9.4 | Backgr  | ound settings                                  | 35 |

|     | 9.4.1   | Background ON/OFF                              | 35 |

|     | 9.4.2   | Background color and brightness                | 35 |

|     | 9.4.3   | Background positioning                         | 35 |

|     | 9.4.4   | Luminance Treshold Yth                         | 36 |

| 9.5 | Positio | ning settings                                  | 37 |

|     | 9.5.1   | Main and sub channel display position          | 37 |

|     | 9.5.2   | The Priority bit                               | 37 |

|     | 9.5.3   | Main and sub channel acquisition position      | 38 |

| 9.6 | Decode  | er settings                                    | 39 |

|     | 9.6.1   | Requirements of the analog input signals       | 39 |

|     | 9.6.2   | Digital decoder settings                       | 41 |

|     | 9.6.3   | Non interlace bit for main and sub             | 43 |

|     | 9.6.4   | 1 Field option                                 | 43 |

|     | 9.6.5   | PAL/NTSC input signal switch                   | 43 |

| 9.7 | Chann   | nel selection                                  | 44 |

|     | 9.7.1   | Numbering of the PIPs in Multi PIP modes       | 44 |

|     | 9.7.2   | Selection of the PIP showing a live picture    | 45 |

|     | 9.7.3   | Fill PIPs with 30% gray picture                | 46 |

|     | 9.7.4   | Example of channel selection with Multi-PIP 16 | 46 |

| 9.8 | Manua   | I mode                                         | 52 |

|     | 9.8.1   | Picture size                                   | 52 |

|     | 9.8.2   | Number of rows                                 | 53 |

|     | 9.8.3   | Number of PIPs in a row                        | 53 |

|     | 9.8.4   | Distances between the PIPs                     | 53 |

|     | 9.8.5   | Horizontal offset for a row                    | 54 |

|     | 9.8.6   | Example of making the Multi-PIP 1-12 mode      | 55 |

|     | 9.8.7   | Example of making a 16:9 PIP                   | 65 |

|     | 9.8.8   | Example of making the subtitle mode            | 70 |

| 9.9 | Televis | sion standard converter (or transcoder)        | 76 |

|     | 9.9.1   | Displaying a PAL signal in a NTSC environment  | 76 |

|    |        | 9.9.2 Displaying a NTSC signal in a PAL environment                                                      |

|----|--------|----------------------------------------------------------------------------------------------------------|

|    | 9.10   | Display settings                                                                                         |

|    |        | 9.10.1 D(igital) filter                                                                                  |

|    |        | 9.10.2 Non interlace bit for the display part                                                            |

|    |        | 9.10.3 F(ast) B(lank) Delay                                                                              |

|    |        | 9.10.4 Pedestal level U and V                                                                            |

|    |        | 9.10.5 Field polarity                                                                                    |

|    |        | 9.10.6 PAL/NTSC output signal switch                                                                     |

|    | 9.11   | Output settings                                                                                          |

|    | 9.12   | zoom function                                                                                            |

| 10 | Applic | ation information per pin                                                                                |

|    | 10.1   | TM2, Multistandard or NTSC                                                                               |

|    | 10.2   | Memory (external VDRAM) data bus                                                                         |

|    | 10.3   | Test-Mode data bus                                                                                       |

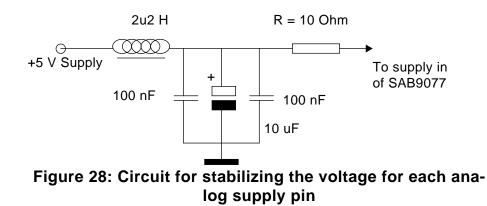

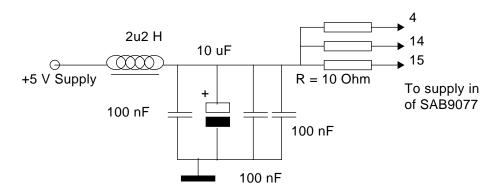

|    | 10.4   | Supply voltages                                                                                          |

|    |        | 10.4.1 Analog supply voltages                                                                            |

|    |        | 10.4.2 Digital supply voltages                                                                           |

|    | 10.5   | Ground                                                                                                   |

|    | 10.6   | Luminance input main and sub91                                                                           |

|    | 10.7   | Color difference inputs U and V, of main and sub                                                         |

|    | 10.8   | Output signals of the display part Y, U and V $\dots \dots \dots \dots \dots \dots \dots \dots \dots 91$ |

|    | 10.9   | IIC inputs                                                                                               |

|    | 10.10  | H-sync inputs                                                                                            |

|    | 10.11  | V-sync inputs                                                                                            |

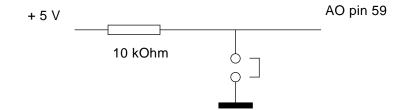

|    | 10.12  | IIC-Address input                                                                                        |

|    | 10.13  | ADC reference signals                                                                                    |

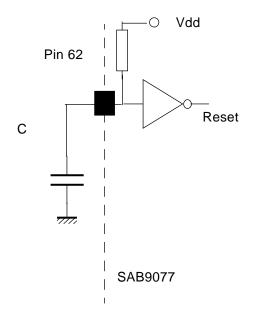

|    | 10.14  | Power on reset                                                                                           |

|    | 10.15  | Fast blank DFB94                                                                                         |

|    |        |                                                                                                          |

### **1** General Description

The SAB9077H is a picture in picture controller for Multi-standard TV-sets. The circuit contains Analog to Digital Converters, reduction circuitry, memory control, display control and Digital to Analog Convertors.

It inserts one or two live video signals with original or reduced sizes into a live video signal. All video signals are expected to be analog base band signals. The conversion into the digital environment and back to the analog environment is done on chip. Internal clocks are generated by two acquisition PLLs and a display PLL.

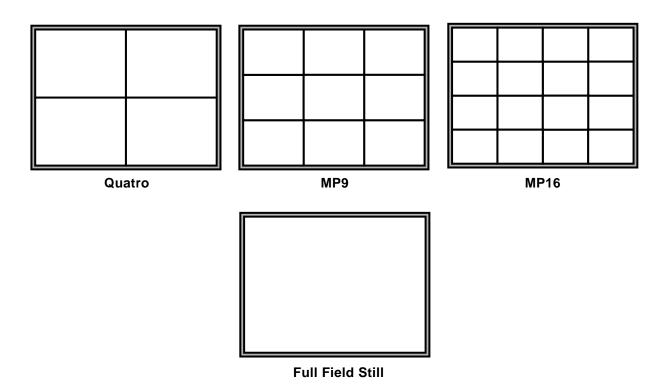

The two PIP channels and a large external memory offer a wide range of PIP modes. The emphasis is put on single PIP, double PIP, Split screen Mode and a many multi PIP modes.

### 2 Features

Display Features are:

- 50/60 Hz pip modes possible

- Twin PIP in interlaced mode at 8-bit resolution

- Sub-Title mode features built in

- Large Display Fine Positioning Area, both channels independent

- Only 2 MB needed as external VDRAM (2 x 1 MB or 1 x 2 MB)

- Four 8 bit AD converters (> 7-bit performance) with Clamp circuit

- Most PIP modes handle interlaced pictures without joint line error

- Two PLLs which generate the line locked clocks for the acquisition channels

- Display PLL to generate line locked clock for the display

- Three 8 bit DA converters

- 4:1:1 data format.

- Data reduction factors 1/1, 1/2, 1/3 and 1/4, horizontal and vertical independent

The following features are programmable via IIC:

- Single and Double PIP modes can be set

- Full Field Still Mode available

- Several aspect ratios can be handled

- Reduction factors can be set freely

- Selection of Vertical Filtering type

- Freeze of live pictures

- Fine tuned Display position, H (8 bit), V (8 bit), both channels independent

- Fine tuned Acquisition area, H (4 bit), V (8 bit), both channels independent

- Eight Main Border (Select), Sub Border (Select) and Background colors available

- Border and Background brightness adjustable, 30%, 50%, 70% and 100% IRE

- Several types of decoder input signals can be set

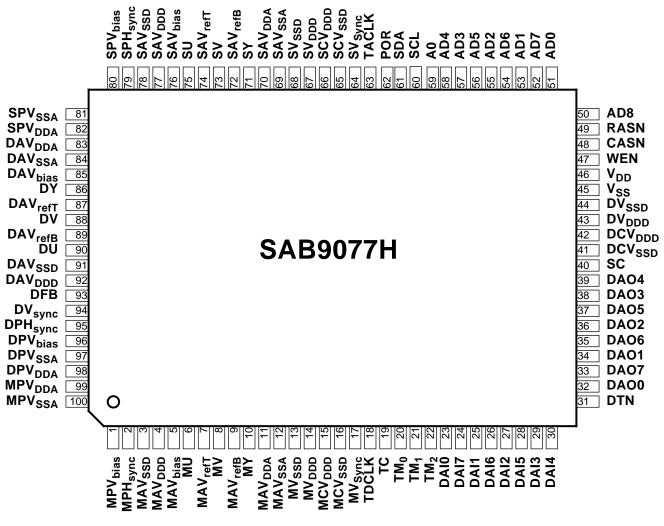

#### **3 Package Outline**

QFP100 (SOT317D8)

Figure 1: Pinning diagram of SAB9077H

## 4 Pinning

| Symbol                                                                                                                                                                      | Pin no.                                            | I/O                                    | Туре                                                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SY<br>SU<br>SV<br>SAV <sub>refT</sub><br>SAV <sub>refB</sub><br>SAV <sub>bias</sub><br>SAV <sub>DDA</sub><br>SAV <sub>SSA</sub><br>SAV <sub>DDD</sub><br>SAV <sub>SSD</sub> | 71<br>75<br>74<br>72<br>76<br>70<br>69<br>77<br>78 | <br> <br> <br> /O<br> /O<br> /O<br> /O | E027<br>E027<br>E027<br>E027<br>E027<br>E030<br>E009<br>E030<br>E009 | Analog Y input of Sub Channel<br>Analog U input of Sub Channel<br>Analog V input of Sub Channel<br>Analog Top Reference for Sub Channel ADCs<br>Analog Bottom Reference of Sub Channel ADCs<br>Analog bias Reference of Sub Channel ADCs<br>Analog V <sub>DD</sub> of Sub Channel ADCs<br>Analog V <sub>SS</sub> of Sub Channel ADCs<br>Digital V <sub>DD</sub> of Sub Channel ADCs and PLLs<br>Digital V <sub>SS</sub> of Sub Channel ADCs and PLLs           |

| SPH <sub>sync</sub><br>SPV <sub>bias</sub><br>SPV <sub>DDA</sub><br>SPV <sub>SSA</sub>                                                                                      | 79<br>80<br>82<br>81                               | <br> /O<br> /O<br> /O                  | HPP01<br>E027<br>E030<br>E009                                        | Horizontal Sync Sub channel<br>Analog bias reference Sub Channel PLL<br>Analog V <sub>DD</sub> of Sub Channel PLL<br>Analog V <sub>SS</sub> of Sub Channel PLL                                                                                                                                                                                                                                                                                                 |

| MY<br>MU<br>MV<br>MAV <sub>ref</sub> B<br>MAV <sub>bias</sub><br>MAV <sub>DDA</sub><br>MAV <sub>SSA</sub><br>MAV <sub>SSD</sub>                                             | 10<br>6<br>8<br>7<br>9<br>5<br>11<br>12<br>4<br>3  | <br> <br> <br> /0<br> /0<br> /0        | E027<br>E027<br>E027<br>E027<br>E027<br>E030<br>E030<br>E030<br>E030 | Analog Y input of Main Channel<br>Analog U input of Main Channel<br>Analog V input of Main Channel<br>Analog Top Reference for Main Channel ADCs<br>Analog Bottom Reference of Main Channel ADCs<br>Analog bias Reference of Main Channel ADCs<br>Analog V <sub>DD</sub> of Main Channel ADCs<br>Analog V <sub>SS</sub> of Main Channel ADCs<br>Digital V <sub>DD</sub> of Main Channel ADCs and PLLs<br>Digital V <sub>SS</sub> of Main Channel ADCs and PLLs |

| MPH <sub>sync</sub><br>MPV <sub>bias</sub><br>MPV <sub>DDA</sub><br>MPV <sub>SSA</sub>                                                                                      | 2<br>1<br>99<br>100                                | <br> /O<br> /O                         | HPP01<br>E027<br>E030<br>E009                                        | Horizontal Sync Main Channel<br>Analog bias reference Main Channel PLL<br>Analog V <sub>DD</sub> of Main Channel PLL<br>Analog V <sub>SS</sub> of Main Channel PLL                                                                                                                                                                                                                                                                                             |

| SV <sub>sync</sub><br>MV <sub>sync</sub><br>DV <sub>sync</sub>                                                                                                              | 64<br>17<br>94                                     | <br> <br>                              | HPP01<br>HPP01<br>HPP01                                              | Vertical sync Sub Channel<br>Vertical sync Main Channel<br>Vertical sync Display channel                                                                                                                                                                                                                                                                                                                                                                       |

| SDA<br>SCL<br>A0<br>POR                                                                                                                                                     | 61<br>60<br>59<br>62                               | I/O<br>I<br>I<br>I                     | IOI41<br>HPF01<br>HPF01<br>HUP07                                     | Shift in data IIC bus, ACK out IIC bus<br>Shift clock for IIC bus<br>IIC address select pin<br>Power on Reset                                                                                                                                                                                                                                                                                                                                                  |

| TM(2)                                                                                                                                                                       | 22                                                 | I/O                                    | HOU21                                                                | Test Mode pin, Input level selection                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TM <sub>(1:0)</sub><br>TC<br>TDCLK<br>TACLK                                                                                                                                 | 21/20<br>19<br>18<br>63                            | <br> <br>                              | HPP01<br>HPP01<br>HPP01<br>HPP01                                     | Test mode pins<br>Test Control<br>Test Clock Display<br>Test Clock Acquisition                                                                                                                                                                                                                                                                                                                                                                                 |

| SC<br>DTN<br>WEN<br>CASN<br>RASN<br>DAI(7:0)<br>DAO(7:0)<br>AD(8:0)                                                                                                                                                                                       | 40<br>31<br>47<br>48<br>49<br>23-30<br>32-39<br>50-58                            | 00000100                                                           | OPF20<br>OPF20<br>OPF20<br>OPF20<br>OPF20<br>HPP01<br>OPF20<br>OPF20                                 | Memory Shift Clock<br>Memory Data Transfer<br>Memory Write Enable<br>Memory Column Address Strobe<br>Memory Row Address strobe<br>Memory to SAB9077H input data bus (7:0)<br>SAB9077H to Memory output data bus (7:0)<br>Memory address bus (8:0)                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SV <sub>DDD</sub><br>SV <sub>SSD</sub><br>MV <sub>DDD</sub><br>DV <sub>DDD</sub><br>DV <sub>SSD</sub><br>V <sub>DD</sub><br>V <sub>SS</sub><br>SCV <sub>DDD</sub><br>SCV <sub>SSD</sub><br>MCV <sub>DDD</sub><br>MCV <sub>SSD</sub><br>DCV <sub>DDD</sub> | 67<br>68<br>14<br>13<br>43<br>44<br>46<br>45<br>66<br>65<br>15<br>16<br>42<br>41 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | E030<br>E009<br>E030<br>E030<br>E009<br>E030<br>E009<br>E030<br>E009<br>E030<br>E009<br>E030<br>E009 | Digital $V_{DD}$ Sub Channel Core<br>Digital $V_{SS}$ Sub Channel Core<br>Digital $V_{DD}$ Main Channel Core<br>Digital $V_{SS}$ Main Channel Core<br>Digital $V_{DD}$ Display Core<br>Digital $V_{SS}$ Display Core<br>Digital $V_{DD}$ Periphery<br>Digital $V_{SS}$ Periphery<br>Digital $V_{DD}$ of Sub Clock buffer<br>Digital $V_{SS}$ of Sub Clock buffer<br>Digital $V_{DD}$ of Main Clock buffer<br>Digital $V_{SS}$ of Main Clock buffer<br>Digital $V_{SS}$ of Main Clock buffer<br>Digital $V_{SS}$ of Display Clock buffer |

| DFB                                                                                                                                                                                                                                                       | 93                                                                               | 0                                                                  | OPF20                                                                                                | Fast Blanking Control signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DY<br>DU<br>DV<br>DAV <sub>refT</sub><br>DAV <sub>refB</sub><br>DAV <sub>bias</sub><br>DAV <sub>DDA</sub><br>DAV <sub>SSA</sub><br>DAV <sub>SSD</sub>                                                                                                     | 86<br>90<br>88<br>87<br>89<br>85<br>83<br>84<br>92<br>91                         | 0<br>0<br>1<br>1<br>1/0<br>1/0<br>1/0                              | E027<br>E027<br>E027<br>E027<br>E027<br>E027<br>E030<br>E030<br>E030<br>E030                         | Analog Y output of DAC<br>Analog U output of DAC<br>Analog V output of DAC<br>Analog Top Reference for DACs<br>Analog Bottom Reference for DACs<br>Analog Voltage Reference DACs<br>Analog V <sub>DD</sub> of DACs<br>Analog V <sub>SS</sub> of DACs<br>Digital V <sub>DD</sub> of DACs                                                                                                                                                                                                                                                 |

| DPH <sub>sync</sub><br>DPV <sub>bias</sub><br>DPV <sub>DDA</sub><br>DPV <sub>SSA</sub>                                                                                                                                                                    | 95<br>96<br>98<br>97                                                             | <br> /O<br> /O<br> /O                                              | HPP01<br>E027<br>E030<br>E009                                                                        | Horizontal Sync Display PLL<br>Analog bias reference Display PLL<br>Analog V <sub>DD</sub> of Display PLL<br>Analog V <sub>SS</sub> of Display PLL                                                                                                                                                                                                                                                                                                                                                                                      |

Pin Type explanation:

| E030 | $V_{DD}$ pin, diode to $V_{SS}$ |

|------|---------------------------------|

|------|---------------------------------|

- E009

- $V_{SS}$  pin, diode to  $V_{DD}$  Analog Input pin, Diode to  $V_{SS}$  and  $V_{DD}$ E027

- Digital input pin, CMOS levels, diode to V<sub>DD</sub> and V<sub>SS.</sub> HPP01

- Digital output pin, CMOS levels. OPF20

- Digital input pin, CMOS levels, diode to  $V_{SS}$ HPF01

- IOI41 IIC pull-down output stage, CMOS input levels, diode to V<sub>SS</sub>.

- Digital input pin, CMOS levels with hysteresis, pull up resistor to V<sub>DD</sub>, diode to V<sub>DD</sub> and V<sub>SS</sub>. HUP07

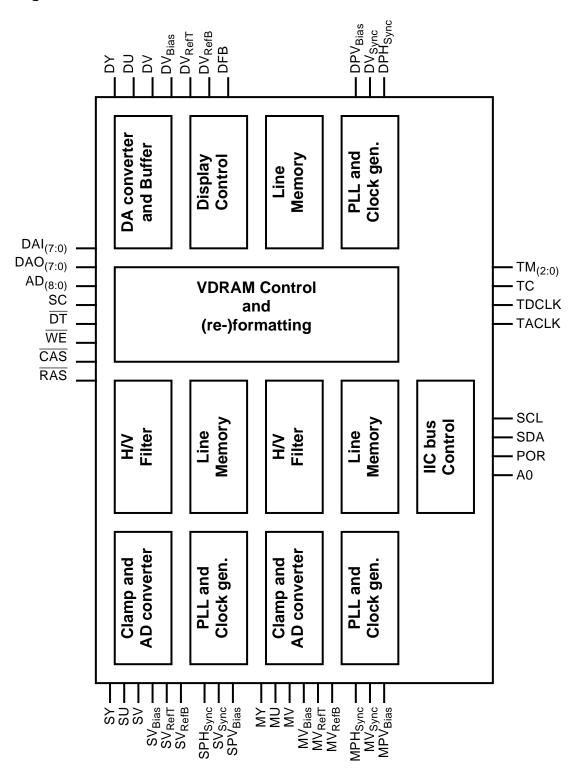

#### **5 Block Diagram**

Figure 2: Block diagram of SAB9077H

Supply pins are not drawn in the diagram above.

### 6 Functional Description

### 6.1 Pixel rate

The internal Chroma format used is 4:1:1. It is expected that the bandwidth of the input signals is limited to 4.5 MHz for the Y input and 1.125 MHz for the U/V inputs.

The Y input is sampled with a 1728\*HS ( $\approx$  27.0 MHz) clock and is filtered and down sampled to the internal 864\*HS ( $\approx$  13.5 MHz) pixel rate.

The U and V inputs are multiplexed and sampled with a 432\*HS clock and down sampled to the internal 216\*HS ( $\approx$  3.375 MHz) pixel rate.

### 6.2 Acquisition Area

Synchronisation is done via the acquisition  $H_{Sync}$  and  $V_{Sync}$  pins. With the acquisition fine positioning added to a system constant the starting point of the acquisition can be controlled.

The acquisition area is 672 pixels/line and 228 lines/field for NTSC and 276 lines/field for PAL. Both channels Main and Sub are equivalent in handling the data.

#### 6.3 Display mode

The internal display pixel rate is  $864*DPH_{Sync}$  which is 13.5 MHz. This pixel rate is upsampled by interpolation to  $1728*DPH_{Svnc}$  before the DAC stage.

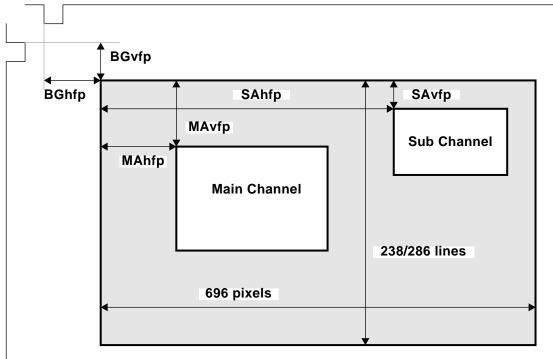

### 6.4 Display Area

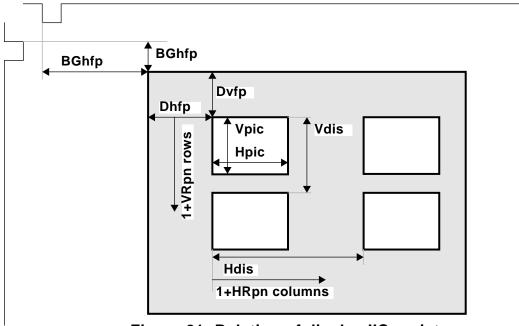

The display background is an area of 696 pixels for both PAL and NTSC, 238 lines for NTSC and 286 lines for PAL. This can be put ON/OFF by the BGON bit independent of the PIPON bits. This area can be moved by the Display Background fine positioning (BGhfp and BGvfp). Its color is determined by the BGCOL and BGBRT bits.

Within this area PIPs are defined dependent on the PIP mode. The PIP sizes are determined by the display reduction factors as is shown in table 1. Whether a PAL or NTSC fixed number is used is dependent on the DPAL bit.

| Reduction  | H1  | H2  | H3  | H4  | V1  | V2  | V3 | V4 |

|------------|-----|-----|-----|-----|-----|-----|----|----|

| pixels     | 672 | 336 | 224 | 168 |     |     |    |    |

| NTSC-lines |     |     |     |     | 228 | 114 | 76 | 57 |

| PAL-lines  |     |     |     |     | 276 | 138 | 92 | 69 |

## Table 1: PIP sizes

The display fine positioning determines the location of the PIPs with respect to the background. Sub Channel and Main Channel both have their independent PIP size and location control. This is depicted in figure 3.

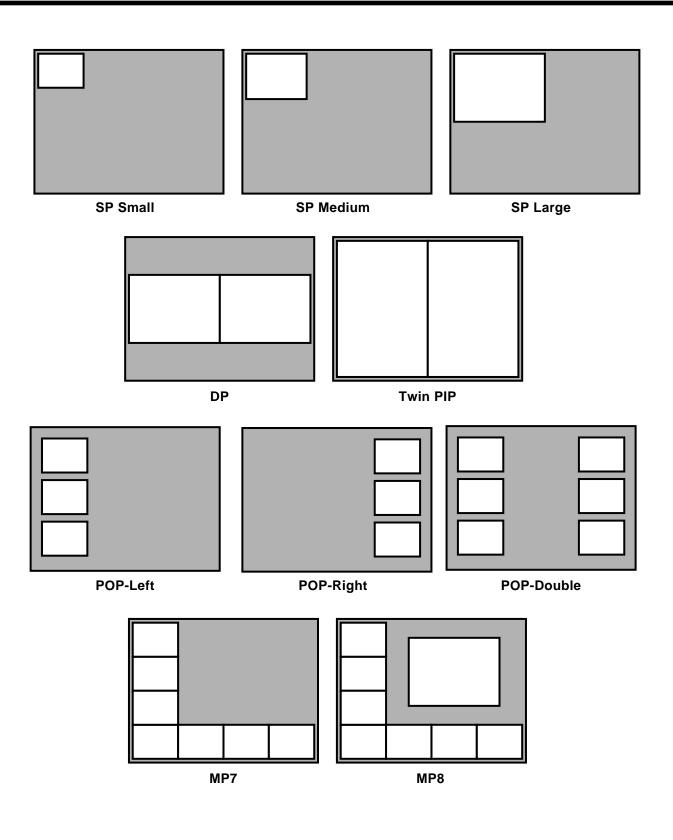

## 6.5 PIP modes

The two independent acquisition channels can also be controlled independently on the display side. A wide variety of modes is possible but a subset of 7 modes is fixed and can be set easily by the IIC bus. An overview of the preconditioned modes is given in table 2.

For all pip modes the Main and Sub display fine positioning must be set to obtain a display configuration.

Figure 3: Display Fine positioning

## 6.5.1 Standard PIP modes

Table 2 shows the standard PIP modes with the settings of the reduction and position factors are displayed.

|      | PIP Modes        | Sub Channel |      | Main C | hannel | Sub C | hannel | Main Channel |     |     |

|------|------------------|-------------|------|--------|--------|-------|--------|--------------|-----|-----|

| Name | Figure           | Mode        | Hred | Vred   | Hred   | Vred  | hfp    | vfp          | hfp | vfp |

| SP   | SP Small         | 0000        | 1/4  | 1/4    | -      | -     | -      | -            | -   | -   |

| SP   | SP Medium        | 0000        | 1/3  | 1/3    | -      | -     | -      | -            | -   | -   |

| SP   | SP Large         | 0000        | 1/2  | 1/2    | -      | -     | -      | -            | -   | -   |

| SP   | SP Small         | 0000        | -    | -      | 1/4    | 1/4   | -      | -            | -   | -   |

| SP   | SP Medium        | 0000        | -    | -      | 1/3    | 1/3   | -      | -            | -   | -   |

| SP   | SP Large         | 0000        | -    | -      | 1/2    | 1/2   | -      | -            | -   | -   |

| DP   | DP               | 0000        | 1/2  | 1/2    | 1/2    | 1/2   | 03h    | 46h          | 57h | 46h |

| DP   | Twin PIP         | 1001        | 1/2  | 1/1    | 1/2    | 1/1   | 03h    | 05h          | 57h | 05h |

| MP3L | POP-Left         | 0010        | 1/4  | 1/4    | -      | -     | 08h    | 10h          | -   | -   |

| MP3R | POP-Right        | 0010        | -    | -      | 1/4    | 1/4   | -      | -            | 72h | 10h |

| MP3D | POP-Double       | 0010        | 1/4  | 1/4    | 1/4    | 1/4   | 08h    | 10h          | 72h | 10h |

| MP7  | POP-Double       | 0011        | 1/4  | 1/4    | -      | -     | 03h    | 05h          | -   | -   |

| MP8  | MP7              | 0011        | 1/4  | 1/4    | 1/2    | 1/2   | 03h    | 05h          | 44h | 20h |

| MP4  | Quatro           | 0001        | 1/2  | 1/2    | 1/2    | 1/2   | 03h    | 05h          | 03h | 77h |

| MP9  | MP9              | 0100        | 1/3  | 1/3    | 1/3    | 1/3   | 03h    | 05h          | 51h | 3Bh |

| MP16 | MP16             | 0101        | 1/4  | 1/4    | 1/4    | 1/4   | 03h    | 05h          | 03h | 05h |

| MP16 | MP16 Mix         | 0110        | 1/4  | 1/4    | 1/4    | 1/4   | 03h    | 05h          | 03h | 77h |

| FFS  | Full Field Still | 0000        | 1/1  | 1/1    | -      | -     | 03h    | 05h          | -   | -   |

| FFS  | Full Field Still | 1000        | -    | -      | 1/1    | 1/1   | -      | -            | 03h | 05h |

| MAN  | Manual           | X111        | х    | х      | x      | х     | х      | x            | x   | х   |

### Table 2: PIP Modes

The pictures 4 and 5 give an overview of possible combinations as they can be shown on the screen. An example of fine positioning is given in the right four columns.

Figure 4: PIP Modes

Figure 5: PIP Modes (continued)

More PiP modes can be obtained by varying the horizontal and vertical reduction factors to meet correct aspect ratios when using 16:9 screens.

In Manual Mode more pipmodes become available. Section "More settings IIC bus" on page 23 describes how to setup a pipmode.

## 7 Device description per functional block

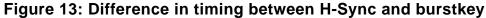

The principle of the working of a Picture-in-Picture is simple. Take a picture, reduce it in size and insert it at the correct position. The first problem that arises is, that broadcasting of different channels is not synchronized. The second problem is that a reduced picture is faster displayed as it will be reduced. For instance, by reducing the picture in the vertical direction with a factor 4, x lines are displayed. For displaying the x lines 4x lines must be processed for each field.

To solve these problems, the data should be buffered and a phase difference of at least one field between the acquiring of a picture and the displaying of the created picture. The data buffer must be able to contain two reduced pictures. As long as data is required for one picture the other one can be displayed. This all holds for one single live PIP. For the buffer a DRAM, SRAM etc can be used.

Two independent live pictures makes two acquisition channels and more memory, then for one live picture necessary. There are three data streams then, two acquired data streams storing data in the memory, and one display data stream retrieving data from the memory.

The SAB9077 is organized in functional blocks (see "Block Diagram" on page 11). These different blocks are:

- PLL and clockgenerator.

- Buffer and clampcircuit.

- ADC.

- H + V Filter.

- VDRAM control and (re-)formatting.

- Data display

- Line memory

- DAC

- Output buffer ad amplifier

- IIC-control

## 7.1 PLL and clockgenerator

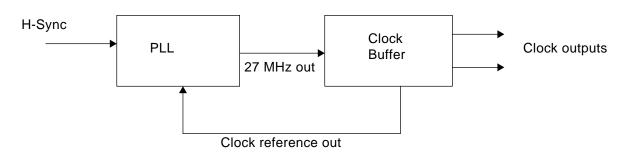

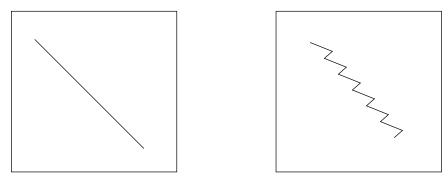

The SAB 9076 has three PLLs on-board, one for the main channel, one for the sub channel and one for the display channel.

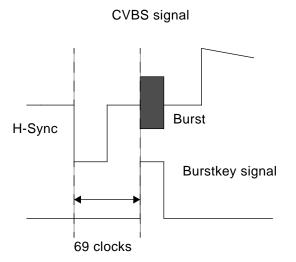

The PLL is used to synchronize the internally used clocksignals with the incoming Horizontal synchronisation signal of a channel (H-sync). The PLL compares the reference output of the clockgenerator with the H-sync signal, produced by the decoder for that channel.

The PLL generates a clock of 27 MHz which is led into the clockbuffer.

The catching range of the PLL is 4 kHz.

Supply voltage Vbias influences the dynamic behaviour of the PLL. Higher Vbias causes the PLL to lock faster, lower Vbias causes the PLL to lock slower.

The positive edges of the H-sync signals are the driving timing points.

## Figure 6: Block diagram of the PLL-circuit

## 7.2 Video-buffer and clamping circuit

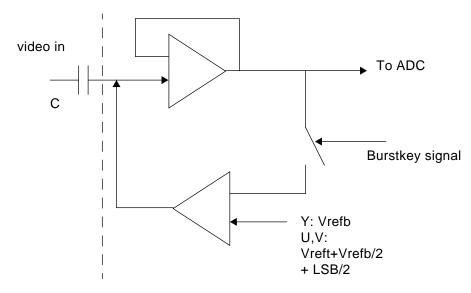

The video-buffer protects the ADC for damage that could be caused by the incoming video signals. The video signals are the Y,U and V output signals of the decoder.

The overall gain of the video-buffer is 1.

The video-buffer bandwidth is 6 MHz.

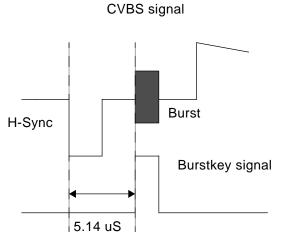

The clamping circuit will clamp the luminance input signal to Vrefb, and the chrominance input signals to Vreft+Vrefb/2 + LSB/2.

The clamping starts at the active edge of the burstkey.

AC-coupling of the video input signal is done outside the PIP-IC with capacitor C, which is also used for clamping.

Figure 7: Video buffer and clamping circuit

## 7.3 Acquisition Channel ADCs

Both channels convert the analog input signals to digital signals by means of a ADCs, one for each channel. The input levels of the ADCs of each channel are equal and can set by the AV<sub>refT</sub> and AV<sub>refB</sub> pins. The reference levels V<sub>refT</sub> and V<sub>refB</sub> are made internally by a resistor division of the VDD. They can be calculated with the formulas V<sub>reft</sub> = AV<sub>DD</sub> x (2.1/5.0) Volt and V<sub>refB</sub> = AV<sub>DD</sub> X (0.4/5.0) Volt

External capacitors are needed to filter AC components on the reference levels. The resolution of the ADCs is 8 bit (DNL is 7 bit, INL is 6 bit) and the sampling is done at the system frequency of 27 MHz for the Y-input. The U/V inputs are multiplexed and sampled at 13.5 MHz.

The analog input signals are amplified to make maximum use of the dynamic range of the ADCs. A bias voltage  $V_{\text{bias}}$  is used for decoupling AC components on internal references. The inputs should be AC-coupled and an internal clamp circuit will clamp the input to  $AV_{\text{refB}}$  for the luminance channels and to  $(AV_{\text{refT}} - AV_{\text{refB}})/2 + LSB/2$  for the chrominance channels. The clamping starts at the active edge of the burst key.

## 7.4 H + V Filters

The horizontal and vertical filters take care that the data that will be stored in the VDRAM have the right dimensions. This means that the horizontal and vertical size are made into the size needed for the chosen PIP mode.

The horizontal filters will compress the picture to the horizontal size of the chosen PIP mode.

The vertical filters will compress the picture to the vertical size of the chosen PIP mode.

## 7.5 VDRAM control and (re-)formatting

## 7.5.1 Memory interface

The SAB9077 consists of three parts, two acquisition channels and a display channel. The acquisition channels filters and decimates the incoming pictures both horizontally and vertically. This depends on the PIPmode that is selected. The result of this process will be formatted from an internal into a 8 bit format which fits in the external VDRAM. The display channel fetches the data from the external VDRAM and reformats it into an internal format again.

The three parts have their own clockdomain and their own VDRAM control. Since only one part at the time may have control over the VDRAM a controller is present to regulate the priorities and the switching over from one VDRAM-controller to another. Furthermore it has to activate a refresh controller, if the acquisition and the display channels are inactive. This controller is the VDRAM-arbiter.

## 7.5.2 VDRAM arbiter

The VDRAM arbiter has four tasks:

- 1. Give the control over the VDRAM to the VDRAM controller of which the request has the highest priority.

- 2. Activate the refresh controller, if none of the others requests the control.

- 3. Switch smoothly from one controller to another, because of the edge sensitivity of the VDRAM.

- 4. Activate the load-address calculator and generate a load pulse for the first line of a channel.

The first time in a field, a controller makes a request, a load address must be calculated. The VDRAM controller signals this to the VDRAM arbiter by a firestone signal. The VDRAM arbiter will activate a central address calculator the dependent of channel type, channel number, system type, horizontal reduction, vertical reduction and internal format use, will determine a loadaddress. This loadaddress connects via a bus to all three address counters. The VDRAM arbiter selects one of them by a load pulse. The load pulse also acts as a reset for the firstline signal. This prevents unnecessary reloading/recalculation. By centralising the generation of the loadaddress, it will be assured that the loadaddress for reading and writing is always the same.

## 7.5.3 external VDRAM

A VDRAM is a normal DRAM which has been modified to ease the handling of video-data. The base of the concept is that video-data most of the time will be handled in blocks in which the pixels have successive numbering. The modification of a normal DRAM is merely adding a large shiftregister that can be accessed almost independently. Furthermore, a lot of block and row oriented modes are present. Only three of them are used by the SAB9077. These modes are:

- **1.** Page write mode.

- 2. Read transfer mode

- 3. CAS before RAS refresh with automatic row addressing.

Most modes work with a Row Access Strobe (RAS), which validates the address, and a Column Access Strobe (CAS), which validates the address as a column address. The VDRAM is sensitive to falling edges of the control signals. With the exception of the shiftclockregister. The shiftclockregister is bidirectional. Data can be shifted out (Read) or shifted in (Write). The type of it will be set by the previous transfer cycle.

For the external memory one VDRAMs of type NEC D482 234 LE-70 is foreseen. It has a storage capacity of 262144 words of 8 bit each.

It is also possible to use two 1MB VDRAM of 262144 words of 4 bit.

### 7.6 Data display

The Data display part takes care of the controls at the display part of the SAB9077.

- The data display part controls:

- **1.** Border (size, color, brightness etc.).

- **2.** Place on the television screen.

- **3.** Line memory control.

- 4. Data stream to the DACs.

- 5. Synchronisation.

## 7.7 Line memory

In the SAB9077 there are four line memories on board. These memories are used to store the data of one line. At the right time, determined by the synchronisation, this memory will be read. The line memories are used to organize the timings in the SAB9077.

The display part uses two line memories. The first line memory is used to write data in, when the second line memory is read. When the second line memory is written, the first line memory is read.

## 7.8 Output DACs

The digital processed signals are converted to analog signals by means of three 8 bit DACs. The output voltages of these DACs are default set by the  $DAV_{refT}$  pin for the top level and  $DAV_{refB}$  pin for the bottom level. Default values are 1.5 V.

## 7.9 Output buffer and amplifier

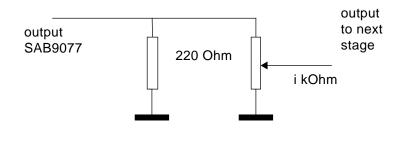

Default signal levels for the output signals DY, DU and DV are 1.5 Vpp. This means that the overall gain of the SAB9077 is 1.

The output signals DY, DU and DV are made lowohmic by means of the output buffers between the DACs and the output pins.

The output load resistors should be 220 to get the overall gain of 1.

The output buffer has a unit voltage gain and a output resistance of 25 Ohm. So when the load resistance Rill = 220 Ohm, the gain is 220/245.

A unit gain is therefore achieved when the DAC input range equals 245/220 times the ADC input range.

DAC (Vreft - Vrefb) =  $245/220 \times 1.7 = 1.9 \text{ V}$ . So Vreft - Vrefb must be 1.9 V, the default values are Vrefb = 0.4 V and Vreft = 2.3 V

For the ADC input range see section "Analog decoder settings" on page 41

## 7.10 IIC bus description

The IIC bus provides bi-directional 2-line communication between different ICs. The SDA line is the serial data line and the SCL serves as serial clock line. Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

The SAB9077H has the IIC addresses 2C and 2E, switchable by the pin A0. Valid sub addresses are 00H to 18H and 20H to 32H. IIC bus control is according to the IIC bus protocol:

First a start sequence must be put on the IIC bus, then the IIC address of the circuit must be send, then a sub address. After this sequence the data of the sub addresses must be send. An auto increment function gives the option to send data of the incremented sub addresses until a stop sequence is send. Table 3 gives an overview of the IIC bus addresses.

| Sub     | Data Bytes |                     |                        |                      |                         |                                              |                                 |                     |  |  |  |  |

|---------|------------|---------------------|------------------------|----------------------|-------------------------|----------------------------------------------|---------------------------------|---------------------|--|--|--|--|

| Address | bit 7      | bit 6               | bit 5                  | bit 4                | bit 3                   | bit 2                                        | bit 1                           | bit 0               |  |  |  |  |

| 00H     | MPIPON     | SPIPON              | MFreeze                | SFreeze              | МСору                   | PiPMode <sub>(2:0)</sub>                     |                                 |                     |  |  |  |  |

| 01H     | -          | -                   | M1FLD                  | S1FLD                | NiPCoff                 | DNonInt                                      | MNonInt                         | SNonint             |  |  |  |  |

| 02H     | DFilt      | FILLOFF             | SMART6                 | SKIP6                |                         | Yth                                          | (3:0)                           |                     |  |  |  |  |

| 03H     |            | BGhf                | P <sub>(3:0)</sub>     |                      |                         |                                              | <sup>f</sup> р <sub>(3:0)</sub> |                     |  |  |  |  |

| 04H     |            |                     |                        | SDhi                 | P(7:0)                  |                                              |                                 |                     |  |  |  |  |

| 05H     |            |                     |                        |                      | P(7:0)                  |                                              |                                 |                     |  |  |  |  |

| 06H     |            |                     |                        | MDh                  | fp <sub>(7:0)</sub>     |                                              |                                 |                     |  |  |  |  |

| 07H     |            |                     |                        |                      | fp <sub>(7:0)</sub>     |                                              |                                 |                     |  |  |  |  |

| 08H     | MDRe       | dH <sub>(1:0)</sub> | MDRe                   | dV <sub>(1:0)</sub>  |                         | dH <sub>(1:0)</sub>                          | SDRe                            | dV <sub>(1:0)</sub> |  |  |  |  |

| 09H     | MARe       | dH <sub>(1:0)</sub> | MARe                   | dV <sub>(1:0)</sub>  | SARe                    | edH <sub>(1:0)</sub> SARedV <sub>(1:0)</sub> |                                 |                     |  |  |  |  |

| 0AH     |            | MAhi                | P <sub>(3:0)</sub>     | i                    |                         | SAhf                                         | p <sub>(3:0)</sub>              |                     |  |  |  |  |

| 0BH     |            |                     |                        | SAvf                 | P(7:0)                  |                                              |                                 |                     |  |  |  |  |

| 0CH     |            |                     |                        |                      | fp <sub>(7:0)</sub>     |                                              |                                 |                     |  |  |  |  |

| 0DH     |            | MLse                | el <sub>(3:0)</sub>    |                      |                         | SLse                                         | el <sub>(3:0)</sub>             |                     |  |  |  |  |

| 0EH     |            | MBs                 | əl <sub>(3:0)</sub>    |                      | SBsel <sub>(3:0)</sub>  |                                              |                                 |                     |  |  |  |  |

| 0FH     |            | Bhsiz               | e <sub>(3:0)</sub>     |                      | Bvsize <sub>(3:0)</sub> |                                              |                                 |                     |  |  |  |  |

| 10H     | -          | SBON                | SBb                    | rt <sub>(1:0)</sub>  | -                       |                                              | SBcol <sub>(2:0)</sub>          |                     |  |  |  |  |

| 11H     | -          | SBSON               |                        | ort <sub>(1:0)</sub> | -                       |                                              | SBScol2 <sub>(2:0)</sub>        | )                   |  |  |  |  |

| 12H     | -          | MBON                | MBb                    | rt <sub>(1:0)</sub>  | -                       | MBcol <sub>(2:0)</sub>                       |                                 |                     |  |  |  |  |

| 13H     | -          | MBSON               | MBSt                   | ort <sub>(1:0)</sub> | -                       |                                              | MBScol <sub>(2:0)</sub>         |                     |  |  |  |  |

| 14H     | -          | BGON                | BGb                    | rt <sub>(1:0)</sub>  | -                       |                                              | BGcol <sub>(2:0)</sub>          |                     |  |  |  |  |

| 15H     | -          | -                   | -                      |                      |                         | SVSPol                                       | SH <sub>sync</sub>              | SFPol               |  |  |  |  |

| 16H     | -          | -                   | -                      | - MVfilt             |                         | MVSPol                                       | MH <sub>sync</sub>              | MFPol               |  |  |  |  |

| 17H     |            |                     | FBdel <sub>(2:0)</sub> |                      | DUVPol                  | DVSPol                                       | DH <sub>sync</sub>              | DFPol               |  |  |  |  |

| 18H     |            | Pedes               | stV <sub>(3:0)</sub>   |                      |                         | Pedes                                        | stU <sub>(3:0)</sub>            |                     |  |  |  |  |

## Table 3: Overview of IIC bus sub addresses

The Data Bits which are not used should be set to zero.

## More settings IIC bus

In Manual mode more PIP modes become available. An overview of these IIC bus registers is given in table 3.

| Sub     | Data Bytes        |                         |                                                                             |                     |                     |                     |                        |                      |  |  |  |

|---------|-------------------|-------------------------|-----------------------------------------------------------------------------|---------------------|---------------------|---------------------|------------------------|----------------------|--|--|--|

| Address | dress bit 7 bit 6 |                         | bit 5 bit 4                                                                 |                     | bit 3               | bit 2               | bit 1                  | bit 0                |  |  |  |

| 20H     | PRIO              | DPal                    | MPal                                                                        | SPal                | MVR                 | pN <sub>(1:0)</sub> | SVRpN <sub>(1:0)</sub> |                      |  |  |  |

| 21H     | MHRp              | O3 <sub>(1:0)</sub>     | MHRp                                                                        | O2 <sub>(1:0)</sub> | MHRp                | 01 <sub>(1:0)</sub> | MHRp                   | 000 <sub>(1:0)</sub> |  |  |  |

| 22H     | MHRp              | N3 <sub>(1:0)</sub>     | MHRp                                                                        | N2 <sub>(1:0)</sub> | MHRp                | N1 <sub>(1:0)</sub> | MHRp                   | 0N0 <sub>(1:0)</sub> |  |  |  |

| 23H     |                   |                         |                                                                             | MHP                 | ic <sub>(7:0)</sub> |                     |                        |                      |  |  |  |

| 24H     |                   |                         |                                                                             | MVP                 | ic <sub>(7:0)</sub> |                     |                        |                      |  |  |  |

| 25H     |                   |                         |                                                                             | MHDi                | s0 <sub>(7:0)</sub> |                     |                        |                      |  |  |  |

| 26H     |                   |                         |                                                                             | MHDi                | s1 <sub>(7:0)</sub> |                     |                        |                      |  |  |  |

| 27H     |                   |                         |                                                                             | MHDi                | s2 <sub>(7:0)</sub> |                     |                        |                      |  |  |  |

| 28H     |                   |                         |                                                                             | MHDi                | s3 <sub>(7:0)</sub> |                     |                        |                      |  |  |  |

| 29H     |                   |                         |                                                                             | MVD                 | is <sub>(7:0)</sub> |                     |                        |                      |  |  |  |

| 2AH     | SHRp              | O3 <sub>(1:0)</sub>     | SHRp                                                                        | 02 <sub>(1:0)</sub> | SHRp                | O1 <sub>(1:0)</sub> | SHRp                   | 000 <sub>(1:0)</sub> |  |  |  |

| 2BH     | SHRpl             | N3 <sub>(1:0)</sub>     | .0) SHRpN2 <sub>(1:0)</sub> SHRpN1 <sub>(1:0)</sub> SHRpN0 <sub>(1:0)</sub> |                     |                     |                     |                        | 0N0 <sub>(1:0)</sub> |  |  |  |

| 2CH     |                   |                         |                                                                             | SHP                 | ic <sub>(7:0)</sub> |                     |                        |                      |  |  |  |

| 2DH     |                   |                         |                                                                             | SVP                 | ic <sub>(7:0)</sub> |                     |                        |                      |  |  |  |

| 2EH     |                   |                         |                                                                             | SHDi                | s0 <sub>(7:0)</sub> |                     |                        |                      |  |  |  |

| 2FH     |                   |                         |                                                                             | SHDi                | s1 <sub>(7:0)</sub> |                     |                        |                      |  |  |  |

| 30H     |                   | SHDis2 <sub>(7:0)</sub> |                                                                             |                     |                     |                     |                        |                      |  |  |  |

| 31H     |                   |                         |                                                                             | SHDi                | s3 <sub>(7:0)</sub> |                     |                        |                      |  |  |  |

| 32H     |                   |                         |                                                                             | SVD                 | is <sub>(7:0)</sub> |                     |                        |                      |  |  |  |

Table 4: Overview of IIC bus sub addresses (continued)

## **8** Application information

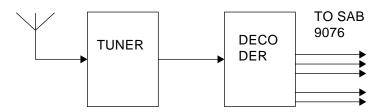

### 8.1 Standard application for 1 FH mode

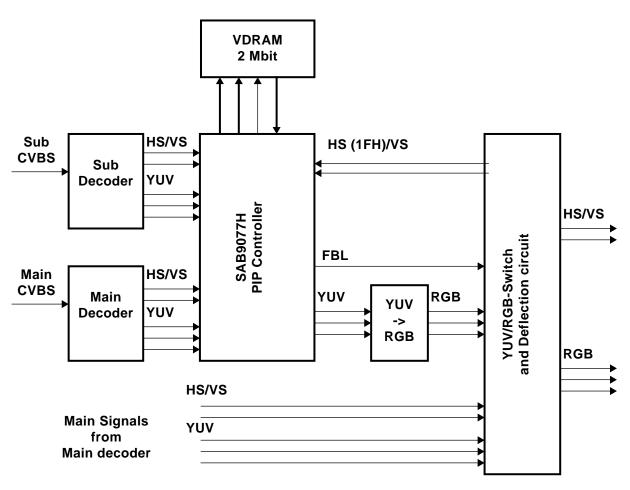

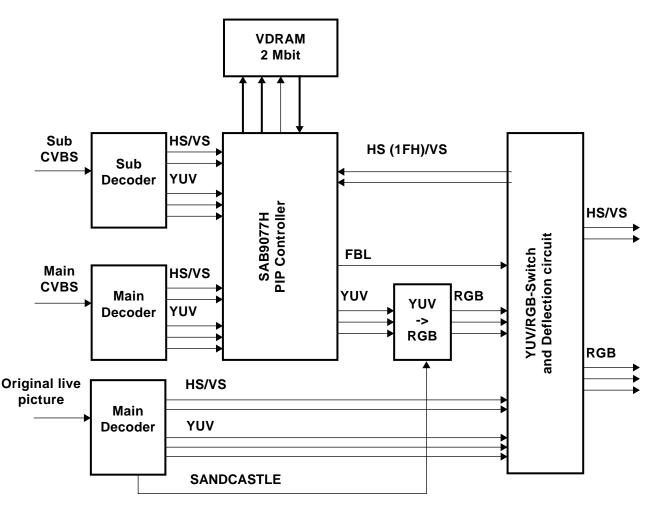

The application diagram for 1 FH mode in a standard configuration is shown in figure 8. Two input signals Main CVBS and Sub CVBS of different sources are processed by the SAB9077H and inserted by the YUV/ RGB switch. The synchronisation of the display PLL is derived from the deflection circuit. The main signals are also led to the deflection circuit and the YUV/RGB switch where the SAB9077H signals can be inserted. The signals for deflection can also be taken from the Main Channel or Sub Channel decoder.

Figure 8: Application diagram 1 FH mode. Main-channel processed as PIP sub channel + one independent sub-channel.

## 8.2 Non standard application for the 1FH mode

The application diagram for 1 FH mode in a non- standard configuration is shown in figure 8 Two input signals Main CVBS and Sub CVBS of different sources are processed by the SAB9077H and inserted by the YUV/ RGB switch. The synchronisation of the display PLL is derived from the Display- circuit. The Display-signals are also led to the deflection circuit and the YUV/RGB switch where the SAB9077H signals can be inserted.

Figure 9: Application diagram 1 FH mode Original live picture as background + two independent PIP-channels.

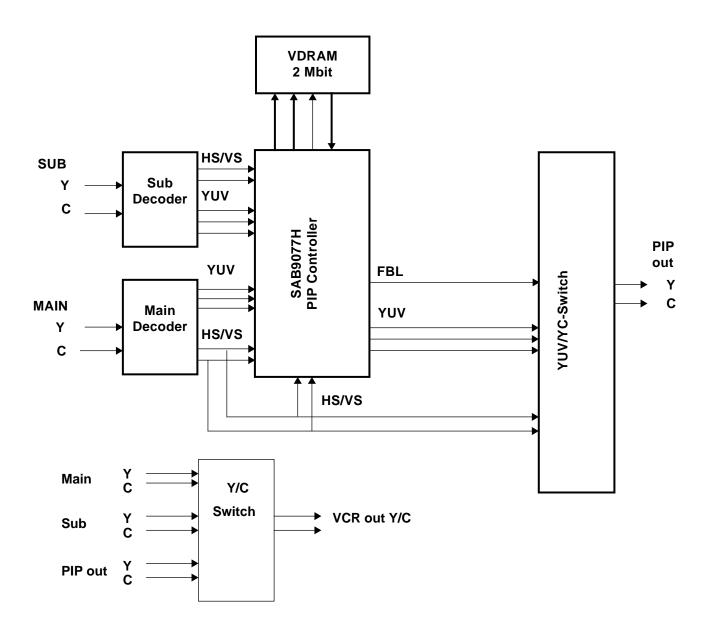

## 8.3 VCR application for the 1 FH mode

The application diagram for 1 FH mode in a VCR configuration is shown in figure 8. Two input signals Main CVBS and Sub CVBS of different video sources are processed by the SAB9077H and inserted by the YUV/ RGB switch. The synchronisation of the display PLL is derived from the Main circuit. The main signals also takes care of the synchronisation of the two video-sources inside the VCR.

The video sources can be two video-signals from one tape or two video signals from two tapes played on the same VCR.

Figure 10: VCR-Application diagram 1 FH mode

## 9 Functionality of the PIP controller SAB9077

The content of the 44 register IIC-bus interface defines the functionality of the PIP controller SAB 9076. The IIC bus interface behaves like a slave receiver device.

## 9.1 PIP modes

## 9.1.1 Enabling the PIP function

After power-up is activated the SAB9077 starts up in the standard mode. In the standard mode all IIC settings are set to 0. So all registers of the IIC settings contain 00 H(exadecimal).

Setting the bit MPIPON (or SPIPON) will activate the Main (Sub) PIP and the Fast Blanking signal (DFB signal). Now the picture in picture signals are merged into the television signal with the help of an external video switch.

## 9.1.2 Standard PIP modes

The controller SAB9077 provides several modes to the TV system. The standard PIP modes can be selected by the mode bits PiPMODE(3, 2, 1, 0) and the reduction bits MDRedH and MDRedV for the main channel, SDRedh and SDRedV for the sub channel.

All these bits should be set properly to get a PIP on the screen. Which PIP will be displayed on the television screen depends on the setting of the bits MPIPON and SPIPON.

The reduction factors Hred and Vred for the main- and sub channel, displayed in table Table 2, "PIP Modes," on page 14, are the same for display and acquisition.

The only difference between the PIP modes MP7 and MP8 is, that in the MP8 mode the main channel PIP is switched ON.

|      | PIP Modes      |      | Sub Channel |      | Main Channel |      | Sub Channel |     | Main Channel |     |

|------|----------------|------|-------------|------|--------------|------|-------------|-----|--------------|-----|

| Name | Figure         | Mode | Hred        | Vred | Hred         | Vred | hfp         | vfp | hfp          | vfp |

| SP   | SP Small       | 0000 | 1/4         | 1/4  | 1/4          | 1/4  | -           | -   | -            | -   |

| SP   | SP Medium      | 0000 | 1/3         | 1/3  | 1/3          | 1/3  | -           | -   | -            | -   |

| SP   | SP Large       | 0000 | 1/2         | 1/2  | 1/2          | 1/2  | -           | -   | -            | -   |

| DP   | DP             | 0000 | 1/2         | 1/2  | 1/2          | 1/2  | 03h         | 46h | 57h          | 46h |

| DP   | Twin PIP       | 1001 | 1/2         | 1/1  | 1/2          | 1/1  | 03h         | 05h | 57h          | 05h |

| MP3D | POP-Double     | 0010 | 1/4         | 1/4  | 1/4          | 1/4  | 08h         | 10h | 72h          | 10h |

| MP7  | POP-Double     | 0011 | 1/4         | 1/4  | -            | -    | 03h         | 05h | -            | -   |

| MP8  | MP7            | 0011 | 1/4         | 1/4  | 1/2          | 1/2  | 03h         | 05h | 44h          | 20h |

| MP4  | Quatro         | 0001 | 1/2         | 1/2  | 1/2          | 1/2  | 03h         | 05h | 03h          | 77h |

| MP9  | MP9            | 0100 | 1/3         | 1/3  | 1/3          | 1/3  | 03h         | 05h | 51h          | 3Bh |

| MP16 | MP16           | 0101 | 1/4         | 1/4  | 1/4          | 1/4  | 03h         | 05h | 03h          | 05h |

| MP16 | MP16 Mix       | 0110 | 1/4         | 1/4  | 1/4          | 1/4  | 03h         | 05h | 03h          | 77h |

| FFS  | FullFieldStill | 0000 |             |      | 1/1          | 1/1  |             |     | 03h          | 05h |

| FFL  | FullFieldLive  | 1000 | -           | -    | 1/1          | 1/1  | -           | -   | 03h          | 05h |

| MAN  | Manual         | X111 | Х           | Х    | Х            | Х    | х           | Х   | x            | х   |

Table 5:PIP Modes

## 9.1.3 Mode bits PiPMode (0, 1, 2, 3)

|      | PIP Modes      |      |  |  |  |  |  |  |  |  |

|------|----------------|------|--|--|--|--|--|--|--|--|

| Name | Mode           |      |  |  |  |  |  |  |  |  |

| SP   | SP Small       | 0000 |  |  |  |  |  |  |  |  |

| SP   | SP Medium      | 0000 |  |  |  |  |  |  |  |  |

| SP   | SP Large       | 0000 |  |  |  |  |  |  |  |  |

| DP   | DP             | 0000 |  |  |  |  |  |  |  |  |

| DP   | Twin PIP       | 1001 |  |  |  |  |  |  |  |  |

| MP3D | POP-Double     | 0010 |  |  |  |  |  |  |  |  |

| MP7  | POP-Double     | 0011 |  |  |  |  |  |  |  |  |

| MP8  | MP7            | 0011 |  |  |  |  |  |  |  |  |

| MP4  | Quatro         | 0001 |  |  |  |  |  |  |  |  |

| MP9  | MP9            | 0100 |  |  |  |  |  |  |  |  |

| MP16 | MP16           | 0101 |  |  |  |  |  |  |  |  |

| MP16 | MP16 Mix       | 0110 |  |  |  |  |  |  |  |  |

| FFS  | FullFieldStill | 0000 |  |  |  |  |  |  |  |  |

| FFL  | FullFieldLive  | 1000 |  |  |  |  |  |  |  |  |

| MAN  | Manual         | X111 |  |  |  |  |  |  |  |  |

Table 6: Standard PIP Modes

The standard in the SAB9077 integrated PIP modes are displayed in table Table 2, "PIP Modes," on page 14. With the bits PiPMode (0, 1, 2, 3) the PIP mode can be selected. The settings for the bits PiPMode and the corresponding PIP mode are displayed in Table 2, "PIP Modes," on page 14

In the manual mode more PIP modes become available. For more information on the manual mode see section "Manual mode" on page 52.

## 9.1.4 Reduction factor settings

The SAB9077 provides several bits to change the reduction factors of the main- and sub channel PIP.

There are two kinds of reduction factors

- **1.** Display reduction factors

- 2. Acquisition reduction factors

Normally the horizontal display- and acquisition reduction factors should be the same. The vertical display reduction factor should be equal or smaller than the vertical acquisition reduction factor. When the horizontal reduction factor is set to 1/1, the vertical reduction factor MUST be set to 1/1

## 9.1.4.1 Main/Sub channel display reduction factors

The display reduction factors determine the size of the PIP on the television screen. Adjustment of the display reduction factor of the main- and sub channel PIP can be done with the bits MDRedH, SDRedH, MDRedV and SDRedV.

| XDRedH | Horizontal display reduction factor in 4 steps. The steps are 1/1, 1/2, 1/3, 1/4. |

|--------|-----------------------------------------------------------------------------------|

| XDRedV | Vertical display reduction factor in 4 steps. The steps are 1/1, 1/2, 1/3, 1/4.   |

| Picture size | XDRedX |   |  |

|--------------|--------|---|--|

| 1/4          | 0      | 0 |  |

| 1/1          | 0      | 1 |  |

| 1/2          | 1      | 0 |  |

| 1/3          | 1      | 1 |  |

## Table 7: Settings of the display reduction factors and obtained picture size.

## 9.1.4.2 Main/sub channel acquisition reduction factors

The acquisition reduction factors determine the size of the picture inside the PIP on the television screen. Adjustment of the acquisition reduction factors of the main- and sub channel can be done with the bits MARedH, SARedH, MARedV and SARedV.

XARedHHorizontal acquisition reduction factor in 4 steps. The steps are 1/1, 1/2, 1/3, 1/4.XARedVVertical acquisition reduction factor in 4 steps. The steps are 1/1, 1/2, 1/3, 1/4.

| Picture size | XARedX |   |  |

|--------------|--------|---|--|

| 1/4          | 0      | 0 |  |

| 1/1          | 0      | 1 |  |

| 1/2          | 1      | 0 |  |

| 1/3          | 1      | 1 |  |

#### Table 8: Settings of acquisition the reduction factors and obtained picture size.

#### 9.1.5 Copy mode

The copy mode is a special mode, needed for the Twin PIP mode.

In the copy mode data of the main channel PIP are not send to the VDRAM. These data are directly routed to the display buffer, after passing the H and V reduction part of the SAB9077.

For this reason the settings of the bits DPAL and MPAL must be the same in the copy mode. If MPAL is set to "1" (PAL), DPAL must also be set to "1" (PAL).

Working this way saves a lot of memory space. If the data of the main channel PIP would be send to the VDRAM, the memory would be too small to make a Twin PIP in 8 bit resolution.

When the copy mode is ON, the vertical acquisition position of the main channel can not be adjusted.

#### 9.1.6 Freeze function

The main- and sub channel can be frozen separately by setting the bits MFREEZE and SFREEZE. The writing to the VDRAM is stopped.

| XFREEZE = 0 | Picture in the PIP is live   |

|-------------|------------------------------|

| XFREEZE = 1 | Picture in the PIP is frozen |

### 9.2 Data transfer settings

The data transfer mode determines the way in which order data is transferred to the external VDRAM. The internal datapath has an 8 bit resolution and 4:1:1 data format. The communication to the external VDRAM takes place at 864 \* H-sync. For display as well as for acquisition.

Appr. 800 8 bit words can be fetched from the external VDRAM in one display line which is not enough to display one complete display line with true 8 bit resolution. Two ways of reducing data are available. One is simply skipping the 8 bit to 6 bit (SKIP6 IIC bit) and the other one is a small form of data reduction to come from 8 bit to 6 bit (SMART6 IIC bit). If both bits are '0' the device is in true 8 bit resolution mode.

The data transfer mode can be selected with the bits SMART6 and SKIP6. The SAB9077 is in the 8-bit mode after start-up.

Selection of the data transfer modes with the bits SKIP6 and SMART6

| D.T.MODE | SMART6 | SKIP6 |

|----------|--------|-------|

| 8 bit    | 0      | 0     |

| smart 6  | 1      | 0     |

| skip 6   | 0      | 1     |

## Table 9: Settings of SMART6 and SKIP6 and the obtained data transfer mode

For the Twin PIP mode the main channel is not placed in the VDRAM but in an internal buffer, see 9.1.5 "Copy mode" on page 29.

#### 9.3 Border settings

The SAB9077 provides several bits to generate a border around the displayed PIPs. Features of this generated border are:

- 1. The border can be switched ON or OFF.

- 2. The border color and brightness can be adjusted.

- 3. The border can be changed in size, that means height and width can be adjusted.

One PIP for the main- and the sub channel can be selected and accentuated with a different color, with the Main (Sub) border select. E.g. to show which PIP displays the live picture, or to point out which picture in the Multi PIP mode should become the live picture on the television screen. Features border select:

- 1. The border select can be switched ON or OFF

- 2. The color of the border select can be adjusted.

- 3. The selected PIP, around which the border select is placed can be changed, to indicate a certain PIP.

### 9.3.1 Border ON/OFF

The borders around the Main- or Sub PIPs can be switched ON or OFF with the bits MBON and SBON.

| XBON = 0 | Border is set to off. |

|----------|-----------------------|

| XBON = 1 | Border is set to on.  |

The border will start at the same point where the displaying of the PIPs starts.

In single PIP modes the start-point of the borders is determined by the horizontal and vertical fine positioning (bits XDhfp and XDvfp).

In Multi PIP modes the start-point of the border around PIP 0 is determined by the horizontal and vertical fine positioning (bits XDhfp and XDvfp). The borders around the other PIPs will be calculated from the start-point of the PIP.

When the size of the borders is changed picture data of lines and pixels will be changed into border data towards the centre. How much lines and pixels are changed depends on the setting of the border-size.

## 9.3.2 Border color and brightness

The brightness and color of the main- and sub channel border is adjustable with the bits MBBRT, MBCOL, SBBRT and SBCOL.

Brightness bit XBBRT: 4 steps 30%, 50%, 70%, 100%. color bit XBCOL: 8 steps black, blue, red, magenta, green, cyan, yellow, white.

Totally there are 8 colors in 4 degrees of brightness each, this means totally 32 colors. By setting the DUVpol to 1 another 32 colors come available, but the color of the background is then also restricted to this 32 colors, see "Polarity of the border and background colors" on page 34

Table 10 indicates how IIC register settings control the color and brightness. All color registers are similar, they contain one On/Off bit, two brightness bits and three color type bits.

| Color Type |       | Brightness level |     |     |      |

|------------|-------|------------------|-----|-----|------|

| Color      | Value | 4-H              | 5-H | 6-H | 7-H  |

| Black      | -0H   | 0%               | 10% | 30% | 50%  |

| Blue       | -1H   | 30%              | 50% | 70% | 100% |

| Red        | -2H   | 30%              | 50% | 70% | 100% |

| Magenta    | -3H   | 30%              | 50% | 70% | 100% |

| Green      | -4H   | 30%              | 50% | 70% | 100% |

| Cyan       | -5H   | 30%              | 50% | 70% | 100% |

| Yellow     | -6H   | 30%              | 50% | 70% | 100% |

| White      | -7H   | 60%              | 70% | 80% | 100% |

### Table 10: Color Types and Brightness levels

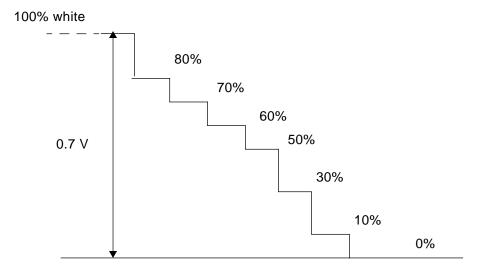

Black and white do not contain any chrominance information. This means that black and white only contain luminance information and are no real colors. That means that a 30% white and a 30% black will show the same gray picture.

Now the ranges of black and white can be fit together to make one gray scale. All the values in this gray-scale are measured as function of the 100% white level. The gray scale is shown in figure 11.

## Figure 11: Gray scale of the values of black and white brightness

#### 9.3.3 border-size

The register 0FH controls the border-size. This implies that border-sizes of the main- and sub channel are changed at the same time, which means that all borders have the same size.

The minimum horizontal border-size is 2 pixels,. The minimum vertical border-size is 1 line.

The vertical border-size is multiplied by the FH mode number before it is displayed on the screen. This means in the 2 FH mode the border-size is 2\* the border-size in 1FH mode.

Horizontal border-size Bhsize : 16 steps of 2 pixels. So maximum horizontal border-size is 32 pixels. Vertical border-size Bvsize : 16 steps of 1 line. So maximum vertical border-size is 16 lines.

When the size of the border becomes bigger, picture data of lines and pixels will be changed into bordered towards the centre. How much lines and pixels are changed depends on the setting of the border-size.

### 9.3.4 Border select

One PIP of the Main channel as well as one PIP of the Sub channel can be given a different color. For example to indicate which PIP shows the live picture at the moment. The Main border select is controlled with MBSON (For Sub channel: SBSON).

| SBSON = 0 | Border select is OFF. |

|-----------|-----------------------|

| SBSON = 1 | Border select is ON.  |

The PIP around which the border select is placed, can be selected with the  $SBsel_{(0:3)}$  bits. To enable selection, SBSON must be '1'.

| SBsel | Border selected |  |

|-------|-----------------|--|

| 0 H   | 0               |  |

| 1H    | 1               |  |

| 2 H   | 2               |  |

| 3 H   | 3               |  |

| 4 H   | 4               |  |

| 5 H   | 5               |  |

| 6 H   | 6               |  |

| 7 H   | 7               |  |

| 8 H   | 8               |  |

| 9 H   | 9               |  |

| AH    | 10              |  |

| ВH    | 11              |  |

| СН    | 12              |  |

| DH    | 13              |  |

| EH    | 14              |  |

| FH    | 15              |  |

Table 11: Border selection with SBsel

The color of the border select is determined by the bits MBSbrt and MBScol, in he same way as explained for the border color and brightness (see "Border Colour and brightness" on page 36).

Television channel selection in a multi PIP mode can be made with the border select.

- 1. On the television screen choose the television channel that should become the live picture with the border select.

- 2. The uP that controls the SAB9077, can select the right channel now, with the latest data send to the XLsel register 0D H.

## 9.3.5 Border priority

To determine which color is visible in case two or more colors will be displayed on the same position the next priority scheme is followed:

- 1. Sub Select Color (SBS)

- 2. Sub Border Color (SB)

- 3. Main Select Color (MBS)

- 4. Main Border Color (MB)

- 5. Background Color (BG)

Sub Select Color has priority over Sub Border Color because otherwise the selected border will have the same color as the other borders.

The priority of Sub over Main is determined by the priority bit, see section "Priority bit" on page 37.

#### 9.3.6 Polarity of the border and background colors

The U,V polarity of the border and background colors can be inverted with the bit DUVpol.

DUVpol = 0U, V polarity.DUVpo = 1-U, -V polarity.

### 9.4 Background settings

The SAB9077 provides several bits to generate a background behind the PIPs. The background has a fixed size 696 pixels and 238 lines, if there is no other PIP or framing information. Features of the background:

1. Background can be switched ON or OFF.

- 2. Background positioning can be adjusted

- **3.** Background color can be adjusted

- **4.** Background transparency can be adjusted

## 9.4.1 Background ON/OFF

The background can be switched ON or OFF with the bit BGON.

BGON = 0 Background switched OFF.

BGON = 1 Background switched ON.

## 9.4.2 Background color and brightness

The brightness and color of the background is adjustable with the bit settings BGbrt and BGcol. Brightness bits MBBRT : 4 steps 30%, 50%, 70%, 100%. Color bits MBCOL : 8 steps black, blue, red, magenta, green, cyan, yellow, white.

Totally there are 8 colors in 4 degrees of brightness each, this means totally 32 colors. By setting the DUVpol to 1 another 32 colors come available, but the color of the borders are then also restricted to this 32 colors, see "Polarity of the border and background colors" on page 34.

Table 10 indicates how IIC register settings control the color and brightness. All color registers are similar, they contain one On/Off bit, two brightness bits and three color type bits.

| Color Type |       | Brightness level |     |     |      |

|------------|-------|------------------|-----|-----|------|

| Color      | Value | 4-H              | 5-H | 6-H | 7-H  |

| Black      | -0H   | 0%               | 10% | 30% | 50%  |

| Blue       | -1H   | 30%              | 50% | 70% | 100% |

| Red        | -2H   | 30%              | 50% | 70% | 100% |

| Magenta    | -3H   | 30%              | 50% | 70% | 100% |

| Green      | -4H   | 30%              | 50% | 70% | 100% |

| Cyan       | -5H   | 30%              | 50% | 70% | 100% |

| Yellow     | -6H   | 30%              | 50% | 70% | 100% |

| White      | -7H   | 60%              | 70% | 80% | 100% |

## 9.4.3 Background positioning

The position of the background can be adjusted within certain limits. The bits  $BGhfp_{(3:0)}$  and  $BGhvp_{(3:0)}$  control the adjustment of the background position.

Horizontal position  $BGhfp_{(3:0)}$ : 16 steps of 4 pixels. So the maximum adjustment range is 64 pixels. Vertical position  $BGvfp_{(3:0)}$ : 16 steps 0f 2lines/field. So the maximum adjustment range is 36 lines/field.

This means the background can be shifted 64 pixels horizontally and 32 lines/field vertically.

## 9.4.4 Luminance Threshold Yth

Luminance threshold means that the original live picture (partially) can be seen through the PIPs.

The level of transparency is set with  $Yth_{(3:0)}$ .

With  $Yth_{(3:0)}$  the slicing level is adjusted. All luminance levels beneath the slicing level will be cut out and filled with the original live picture.

Yth = 0 HNo transparency, so nothing of the original live picture can be seen through the PIPs.Yth = F HMaximum transparency, the original live picture can be seen through the PIPs

If  $Yth_{(3:0)}$  becomes maximum, the fast blank signal is switched off and the original live picture will be visible.

If borders are used around the PIPs, the borders will remain visible, even when Yth is set to maximum. The fast blank signal is not switched off.

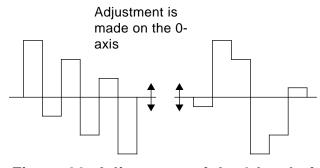

If a back ground is used, the original live picture can be seen through the PIPs, not through the background. The fast blank signal is not switched off.